## LPC2388内蔵Ethernetコントローラで採用されている

## 論理層と物理層をつなぐ インターフェースRMII

松本 信幸

## ● Ethernet における MII

Ethernet における物理層は実に多様です。通信を行う距離や速度といった使用目的に応じて、ツイスト・ペア・ケーブル、同軸ケーブル、光ファイバ・ケーブルなどの選択肢があります。

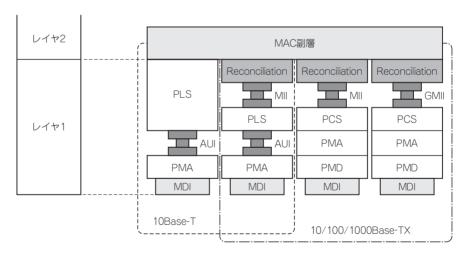

この多様な選択肢を実現している手法の一つに, 論理層 (MAC) と物理層 (PHY) の機能を明確に切り離し, 内部インターフェース仕様を規定していることがあります.

この内部インターフェースを、MII (Media Independent Interface)と称します。文字通りメディア、すなわち接続するケーブルや通信速度の種類から MAC 層を独立させるインターフェースです (図 A)。MII で使われる信号は表 A に示すように合計 16 本 (マネージメント制御系信号を除く)です。

MII には、10Mbps と 100Mbps に対応している MII のほかに、G ビット Ethernet である 1000M (1G) bps に対応可能な

GMII, さらに高速な 10Gbps にも対応可能な XMII があります.

## ● LSI から見た MII の在り方

昨今は、これまでネットワークとは無縁だった組み込み機器にも Ethernet 通信機能が要求されるようになってきました.ワンチップ・マイコンで使用される LSI パッケージは、(PIC マイコンのような DIP パッケージのものを除けば) 小さいもので 64 ピン、大きいものなら 144 ピン程度の QFP (Quad Flat Package)が使われています.これらのピン数の中に、電源やグラウンド・ピンはもちろん、多数の A-D/D-A 入出力や汎用 I/O、PWM 出力、シリアル入出力ピンを割り当てる必要があります.このような中に MII を入れようとすると、16 本という信号本数は大きな割合を占めることになります.

また、スイッチング・ハブのようなネットワーク機器では、 複数のポート間でパケットの入出力を同時に行うため、ASIC

図 A Ethernet のレイヤ構成

表 A MII 信号一覧 (方向は論理層から 見たとき)

| グループ    | 信号名称          | 方向  | 意味                      |

|---------|---------------|-----|-------------------------|

| 受信系     | RX_CLK        | 入力  | 受信クロック                  |

|         | RX_DV         | 入力  | 受信フレームを検出したとき '1'       |

|         | $RXD0 \sim 3$ | 入力  | 受信フレーム・データ (ビット0~3)     |

|         | RX_ER         | 入力  | 受信情報にエラーが認められたとき '1'    |

| 送信系     | TX_CLK        | 入力  | 送信クロック                  |

|         | TX_EN         | 出力  | 送信フレームを出力中は '1' にする     |

|         | $TXD0 \sim 3$ | 出力  | 送信フレーム・データ (ビット0~3)     |

|         | TX_ER         | 出力  | 送信障害通知時に1クロック以上 '1' にする |

| 半2重制御系  | COL           | 入力  | パケット衝突検出時 '1'           |

|         | CRS           | 入力  | キャリア検出時 '1'             |

| マネージメント | MDC           | 出力  | マネージメント用クロック出力          |

| 制御系     | MDIO          | 入出力 | マネージメント用データ入出力          |