## 徹底 解説 信和認力がるPCI Express

## 第13回 最も基本的なPCI Expressデバイスの設計

内藤 竜治

今回はこれまで設計してきたPCI Expressコアへ簡単なユーザ回路を接続し、最も基本的なPCI Expressデバイスを設計する. そして設計したデバイスに対して、PCIデバッグ・ライブラリを使ってコンフィグレーション・レジスタやメモリを読み書きする. (編集部)

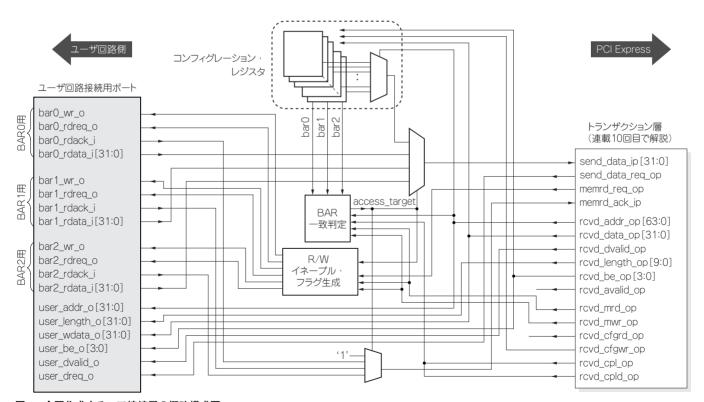

本連載で説明してきた、トランザクション層とユーザ回路との間をつなぐ部分をコア接続層と呼ぶことにします。コア接続層は図1のような構造をしています。この中にはコンフィグレーション・レジスタやメモリ・アクセスのヒット条件を判定する回路が入ります。しかし、コア接続層の具体的な動作はPCI Express の規格では定義されていないので、ここから先はオリジナルの方法で実装を考えることになります。

## 1. コンフィグレーション空間の実装

## ● コンフィグレーション・リードの実装

前回 (本誌 2010 年 3 月号, pp.182-191) と前々回 (同 2 月 号, pp.157-167) で説明したように、PCI Express のエンド ポイントには、さまざまなコンフィグレーション・レジス タがあります。まずは VHDL でこれらのレジスタを宣言 するところから始めましょう (リスト 1).

トランザクション層は、ルート・コンプレックスからコ ンフィグレーション・リード・リクエストを受信すると、

図1 今回作成するコア接続層の概略構成図

トランザクション層とユーザ回路をつなぐのが主な役割.複雑なロジックはなく,セレクタやアドレスの一致判定回路などがある.