Interface編集部

2024年12月号別冊付録 GOWIN Vol.4サポートページ

誌面に掲載できなかった情報やダウンロード・データについて掲載します.

●1章 Arora Vを搭載したボード

参考文献

・Sipeed Tang Primer 25K ダウンロードサイト

●1部1章 GOWIN EDAの便利機能

▲開発構築と新規プロジェクトの作り方

▲ビルド時の設定

・HDLの設定

GOWIN EDAは複数のHDLを扱えます.デフォルトではソースコードをVerilogとして解釈するような設定になっているので,本誌の内容を試す場合には,SystemVerilog用に設定してから合成を行います.

メニューから,「Project」-「Configuration」とクリックし,開いたダイアログの左側から,「Synthesize」-「General」をクリックします.右側のVerilog Language:でSystem Verilog 2017を選択します.

・ピンの設定

FPGAでは,1つのピンに複数の機能が割り当てられている場合があります.そのようなピンをI/Oに使用していると,合成時にエラーが出ることがあります.次のページで,ピンをI/O専用として設定することで,エラーを回避できます.

「Project」-「Configuration」とクリックし,開いたダイアログの左側から,「Dual-Purpose Pin」をクリックします.

Use MSPI as regular IO や Use CPU as regular IOはチェックした方がよいかもしれません.

▲FPGA内蔵のロジアナ機能GAOの使い方

Vol.3で紹介したGowin Analizer Ascilloscopeの使い方

参考文献

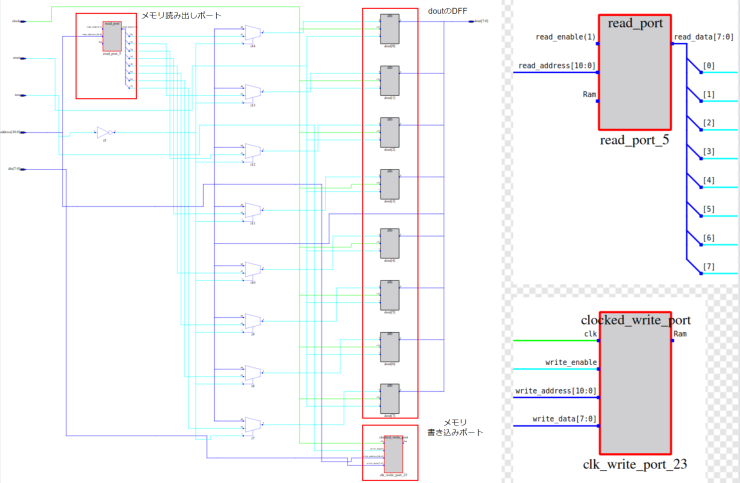

●1部2章 マクロを推論させるコード

▲RTL Viewerで見る合成結果

●1部3章 VALID READY

参考文献

・Avalon Interface Specifications

●2部1章 SPI通信

▲テストベンチのRTLコード

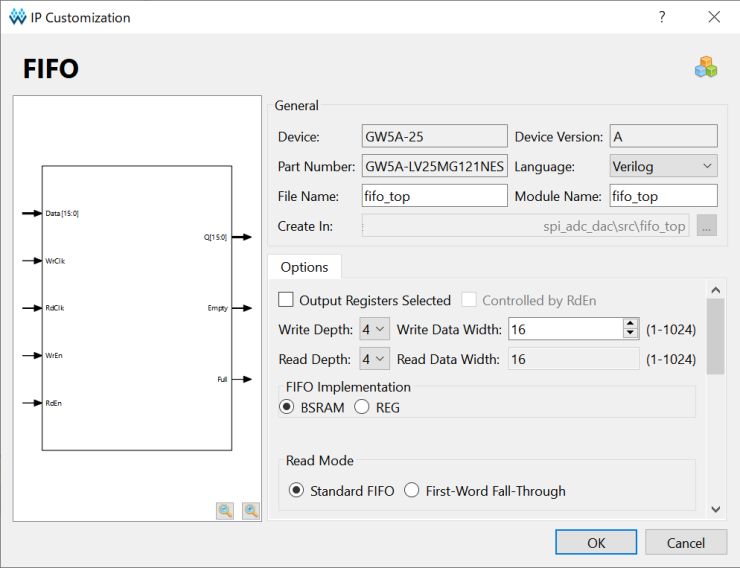

▲FIFOのIP設定画面

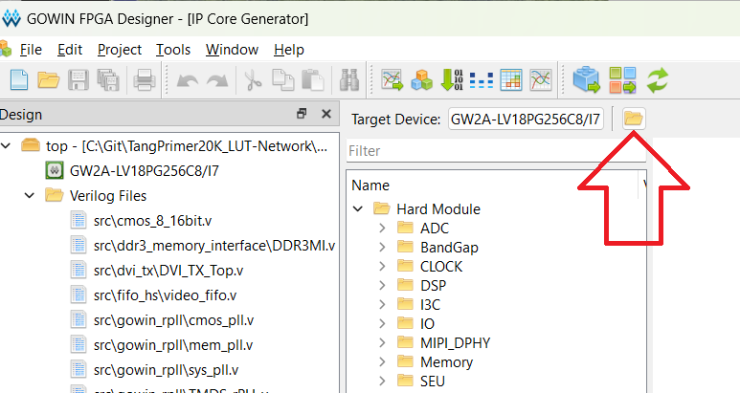

▲IP Core Generatorの使い方

GowinのEDAに含まれるIP Core GeneratorでIPを生成すると,プロジェクトのsrcフォルダに.ipcファイルが自動生成されます.

改めてIP Core Generatorを開いたときに,.ipcファイルを指定すると,以前の設定を呼び出せます.

.ipcファイルの指定は,IP Core Generatorの「フォルダ」アイコンをクリックして行います.

(本稿のダウンロードデータにも,.ipcファイルが含まれています.上記の手順でIPを生成してください)

▲実験の様子

●2部3章 USB基礎

●2部4章 USB実装

▲ダウンロード・データ

参考文献

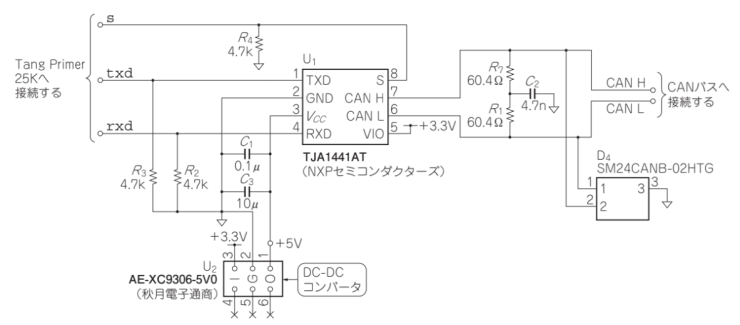

●2部5章 CAN通信

▲実験に使ったCANトランシーバの回路図

▲車載メータの様子

自動車の発信加速をシミュレーションしている

参考文献

・RS485 CAN HAT for Raspberry Pi

●第3部 FPGAでAI

OV2640の使い方については,Interface誌2023年12月号 別冊付録「7000円ボードで始めるFPGA開発Vol.3」の第3部が参考になります.

参考文献